Available Online at http://www.recentscientific.com

**CODEN: IJRSFP (USA)**

International Journal of Recent Scientific Research Vol. 9, Issue, 5(D), pp. 26773-26776, May, 2018 International Journal of Recent Scientific Re*r*earch

DOI: 10.24327/IJRSR

# **Research Article**

## **TAPERING INTERCONNECT TOPOLOGY FOR HIGH SPEED VLSI DESIGN**

### Darshan Halliyavar<sup>1</sup> and Srividya P<sup>2</sup>

<sup>1</sup>VLSI Design and Embedded Systems RV College of Engineering, Bengaluru <sup>2</sup>Department of ECE RV College of Engineering, Bengaluru

DOI: http://dx.doi.org/10.24327/ijrsr.2018.0905.2119

#### **ARTICLE INFO**

Received 17th February, 2018

Received in revised form 21st

Published online 28<sup>th</sup> May, 2018

Interconnect Routings, Modified

Design Rule Check (DRC).

Minimum RC delay, Elmore equations,

Accepted 05<sup>th</sup> April, 2018

Article History:

March. 2018

Key Words:

ABSTRACT

Optimizing the interconnects plays an important role in core CPU architecture to obtain higher speeds. Interconnects consists of RC components, for which decreasing the RC delay plays an Important role. There are many Interconnect topologies but the optimal one helps in obtaining the minimal delay. The paper explains a new interconnect routing technique called Tapering to reduce this delay. Tapering routing topology helps in getting the minimal RC delay. It uses the Elmore delay model to get the minimal RC delay. The right percentage of tapering will fetch optimal results. Further implementation of this topology can be automated and can be effective in improvising the speed. In this technique, the resistance near the driver is made higher and the capacitance near the receiver is lowered. This leads to the improvement in RC delay. At first, the routing is done manually for a small portion of the chip and subsequently it is automated to do the routing for the entire section of the chip. Using the technique, it is observed that RC delay decreases by 10% to 30%.

**Copyright** © **Darshan Halliyavar and Srividya P, 2018**, this is an open-access article distributed under the terms of the Creative Commons Attribution License, which permits unrestricted use, distribution and reproduction in any medium, provided the original work is properly cited.

## **INTRODUCTION**

The scaling of CMOS transistors has led to the improvement in device performance with increased transistor density and reduced power consumption. Scaling of interconnects plays an important role as it reduces the usage of area, power and also resolves the timing issues. To improve the delay aspects of interconnects one has to focus on improving the routing techniques. Thus for this purpose Tapering routing technique has been introduced in this paper to make it a high speed interconnect. This routing technique uses the concept of Elmore delay model which tells that increasing the width near the driver side and decreasing the width near the receiver side helps in decreasing the RC delay. It means that the value of the resistance has to be more near the driver side than that of the receiver side and the capacitance value is vice versa. Further this technique which is developed can also be proved mathematically.

This technique is first done manually for few nets and results are calculated. The design is then automated to test the entire chip with number of nets. By automation, the accuracy increases. Shielding is another technique of adding extra net which is connected to VDD or VSS. This helps in removing the effects of cross coupling capacitance in between the adjacent nets. Thus tapering technique with the combination of shielding i.e. half shielding and full shielding will lead to decrease of RC delay values. Least RC delay for a particular net is obtained by comparing the RC delays obtained for the net using some of the high speed routing techniques like metal strapping and shielding. Further the entire utility can be automated and all the topologies can be compared and tested to obtain the best results.

### Previous Work

With the increase in the operating frequency, the VLSI interconnects becomes critical for the overall system design. There has been active research in optimizing interconnect delays and much progress has been made. Many interconnect models like ideal wire, lumped, distributed models are developed. These models help in modelling the interconnects easily.

In papers[1-4], performance modelling of high speed interconnects are developed and optimization of these interconnects are carried out. The papers also provide information about optimizing global wire widths. The different design objectives and wire length distributions as suggested in the papers can be considered during wire width planning. However, these methods have small amount of errors compared

\*Corresponding author: Darshan Halliyavar

VLSI Design and Embedded Systems RV College of Engineering, Bengaluru

with the optimal solutions. Thus the inference from these papers is that the simplified wire sizing schemes and wire width planning methodology will be very useful for better design convergence and simpler routing architectures.

Paper [8] describes the modelling and simulation of tapered nets for clock distribution networks which helps in reducing the delay. In addition to this the tapering can be done for the ground wires and delay can be obtained. To improve the RC delay of the nets some of the techniques like metal upgradation to higher layers, strapping, widening, shielding can also be done. Some of these techniques are implemented to resolve issues concerned with area, timing and availability of resources. Since interconnect has become a dominant issue in high performance ICs, the focus of the circuit design has been shifted more towards interconnects optimization. An improvement of RC delay was achieved with the help of different combinations of higher layer metals which are of less resistance. Multiple criteria such as delay, power dissipation, noise, bandwidth, and physical area was considered during the interconnect design process.

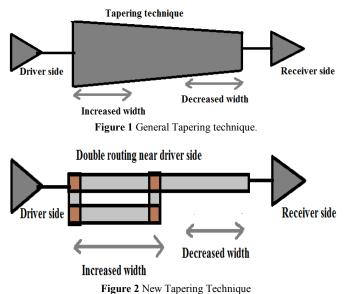

### Tapering techniques

The Elmore delay model, plays an important and huge role in reducing the RC delay. This model cannot be applied to tapering wire technique practically because the wire width at the receiver side and driver side cannot be different. So a new topology is proposed in which double routing is done near driver side and single track routing is done near the receiver side. The conventional and new wire topology are shown in the Figure 1 and Figure 2 respectively.

Figure 2 New Tapering Teeninque

In the proposed new technique, double routing is done near the driver side with tapering of 10% to 50% and end to end simulation results are observed. Tapering percentage plays an important role in RC delay. If tapering percentage increases more than 50% it is observed that there is no eventual decreases in the RC delay. There are chances that it might even lead to increase in RC delay. So the right percentage of tapering should be done. The combination of metal layers also plays a very important role in deciding the RC delay.

## METHODOLOGY

Using custom tools manual implementation of routing is done for some of the nets. An algorithm is developed for automatic tapering technique with their respective set of metal and via attributes. Further the DRC cleaning is done. The DRC cleaning is done manually for each net with help of ICC tool. The tool follows a certain design rule to draw the layout. Thus violations are checked after routing. Some of the issues like via to via, minimum length, shorts, spacing, etc. have to be cleaned. If DRC violations are not cleaned there will be no visible improvement in RC delay. So preventive measures have to be taken to check the DRC violations. Figures 3 and 4 shows the implementation of tapering routing technique done through the ICC tools by manually and automation respectively.

Figure 3 Tapering of the net done manually.

Figure 4 Tapering of the net done through automation

Automatic routing algorithm for tapering technique:

- The algorithm finds the x, y coordinates and the metal layer on which the tapering has to be done.

- If the metal layer for which tapering is to be done is small, then it does not proceed further as there will be no considerable improvement in the RC delay.

- The routing technique is not done to clock net and power nets.

- It checks for the empty space beside the track so that the extra routing can be done easily.

- The extra routing technique is done and via's are placed correctly for the respective metal attributes.

- The procedure is written for cleaning the DRC violations and also checked if any DRC violations are found in the section.

- Then using the IC advisory, the RC delay value is calculated for both the tapered nets and that of non-tapered nets.

- A code is written for the comparison of the both the delay files which are obtained through the IC advisory.

### **RESULTS AND DISCUSSION**

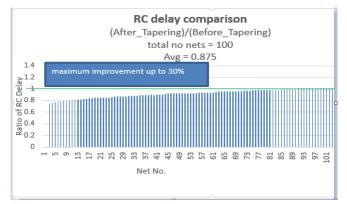

The RC delay of the nets are noted before and after tapering and the difference between the nets are calculated and the percentage improvement are tabulated in Table.1.

| Table 1 Results of 10 nets and their improvement in pe | rcentage |

|--------------------------------------------------------|----------|

|--------------------------------------------------------|----------|

| #Net                          | RC delay before tapering(ps) | after tapering (ps) | improvement in % |

|-------------------------------|------------------------------|---------------------|------------------|

| rseudepmatcheum203h[4][44]    | 0.0197                       | 0.0175              | 11.16            |

| aleubundselm2011[4][2]        | 0.014                        | 0.012               | 14.28            |

| rseudepmatcheum203h[4][42]    | 0.017                        | 0.012               | 29.41            |

| rseudepmatcheum203h[4][54]    | 0.028                        | 0.023               | 17.85            |

| aldispport5m201h[3]           | 0.027                        | 0.02                | 25.95            |

| rseudepmatcheum203h[4][46]    | 0.032                        | 0.028               | 12.5             |

| ooovrpt27e1idlsrcm200h#[1][2] | 0.03                         | 0.026               | 13.33            |

| rseudepmatcheum203h[4][58]    | 0.023                        | 0.02                | 13               |

| ooovrpt49e1rsuopcvrm301h[5]   | 0.025                        | 0.021               | 16               |

For simplicity, only the 10 nets are shown. The RC delay before tapering and after tapering is calculated through the IC advisory which is in picoseconds and the percentage improvement is tabulated in the last column in Table 1.

Figure 5 shows the RC delay comparison of 100 nets of a particular section in a chip. The RC delay that is calculated before and after tapering are plotted to find the improvement in the ratio of RC delay. The RC delay ratio of more than 1 is considered as a worst case, so 1 is considered as demarcation line. Further a maximum decrease of up to 30% is observed in RC delay when compared with the original one. An average value of RC delay ratio is of 0.875.

## CONCLUSION

The work presented in this paper suggests that double routing tapering technique proves effective in decreasing the RC delay. The RC delay decreases by 10% to 30% compared to the original one. Thus this routing technique is suitable for the high speed designs where speed plays a very critical role.

As a future improvement, this routing technique can be also be implemented for the nets having multiple fanouts. Further with several routing techniques a framework can be devloped which automatically helps us to know the better RC delay values.

#### Acknowledgments

Special thanks to Arpit, Basil, Sameer, Prachi and Tanmay for their guidance in routing techniques and in clearing all the DRC violations.

### References

- 1. Q. J. Zhang, F. Wang and M. S. Nakhla, "Optimization of high-speed VLSI interconnects," *1996 Symposium on Antenna Technology and Applied Electromagnetics*, Montreal, QC, Canada, 1996, pp. 265-268.

- Kurokawa, T. Sato, T. Kanamoto and M. Hashimoto, "Interconnect Modeling: A Physical Design Perspective," in *IEEE Transactions on Electron Devices*, vol. 56, no. 9, Sept. 2009, pp. 1840-1851.

- J. V. R. Ravindra and M. B. Srinivas, "Performance modeling of high speed VLSI interconnects," 2010 Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics (PrimeAsia), Shanghai, 2010, pp. 61-64.

- Michel Nakhla, Eli Chiprout, Ramachandra Acha, Roni Khazaka, "Recent Progress in the Simulation of High Speed VLSI Interconnects" *IEEE Trans. Circuits and Syst,* vol 37, Jan.1994, pp. 1-6.

- 5. M.Kavicharan, N.S.Murthy, N. Bheema Rao "An Efficient Delay Estimation Model for High Speed VLSI Interconnects", 2013 International Conference on Advances in Computing, Communications and Informatics (ICACCI), pp. 1358-1362.

- 6. Mal, Ashis Kumar & Dhar, Anindya. (2010). "Modified Elmore delay model for VLSI interconnect", *Midwest Symposium on Circuits and Systems*, pp.793-796.

- Mutlu Avci, Serhan Yamacli, "An improved Elmore delay model for VLSI interconnects, Mathematical and Computer Modelling", Elsievier, Volume 51, Issues 7– 8,2010, pp. 908-914.

- 8. M. A. Karami and A. Afzali-Kusha, "Exponentially Tapering Ground Wires for Elmore Delay Reduction in On Chip Interconnects," 2006 International Conference on Microelectronics, Dhahran, 2006, pp. 99-102.

- 9. J. P. Fishburn and C. A. Schevon, "Shaping a distributed-RC line to minimize Elmore delay," in *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, vol. 42, no. 12, Dec 1995, pp. 1020-1022.

- 10. Jason Cong and Zhigang Pan, "Wire width planning for interconnect performance optimization," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 21, no. 3, Mar 2002, pp. 319-329.

- 11. M. A. El-Moursy and E. G. Friedman, "Optimum wire tapering for minimum power dissipation in RLC interconnects," 2006 IEEE International Symposium on Circuits and Systems, Island of Kos, 2006, pp.485-488.

- 12. R. Kumar, V. Zyuban and D. M. Tullsen, "Interconnections in multi-core architectures: understanding mechanisms, overheads and scaling," *32nd International Symposium on Computer Architecture (ISCA'05)*, 2005, pp. 408-419

- B. Kahng, S. Muddu and E. Sarto, "Interconnect optimization strategies for high-performance VLSI designs," *Proceedings Twelfth International Conference* on VLSI Design. (Cat. No.PR00013), Goa, 1999, pp. 464-469

- 14. P. Ghosh, R. Mangaser, C. Mark and K. Rose, "Interconnect-dominated VLSI design," *Proceedings* 20th Anniversary Conference on Advanced Research in VLSI, Atlanta, GA, 1999, pp. 114-122.

- Fujiwara, M. Koibuchi, H. Matsutani and H. Casanova, "Swap-And-Randomize: A Method for Building Low-Latency HPC Interconnects," in *IEEE Transactions on Parallel and Distributed Systems*, vol. 26, no. 7, pp. 2051-2060,

- Llamas-Garro *et al.*, "Recent trends and considerations for high speed data in chips and system interconnects," 2015 SBMO/IEEE MTT-International Microwave and Optoelectronics Conference (IMOC), Porto de Galinhas, 2015, pp. 1-6

- 17. D. Duvvuri, S. Agarwal and V. S. R. Pasupureddi, "A new hybrid circuit topology for simultaneous bidirectional signaling over on-chip interconnects," 2016 *IEEE International Symposium on Circuits and Systems (ISCAS)*, Montreal, QC, 2016, pp. 2342-2345.

- D. Pandini, C. Forzan and L. Baldi, "Design methodologies and architecture solutions for highperformance interconnects," *IEEE International Conference on Computer Design: VLSI in Computers and Processors, 2004. ICCD 2004. Proceedings.*, 2004, pp. 152-159

- O. Sharma, A. Saini, S. Saini and A. Sharma, "A Quadro Coding Technique to Reduce Self Transitions in VLSI Interconnects," 2016 IEEE International Symposium on Nanoelectronic and Information Systems (iNIS), Gwalior, 2016, pp. 98-101

- 20. Cong and Zhigang Pan, "Interconnect performance estimation models for design planning," in *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 20, no. 6, Jun 2001, pp. 739-752.

#### How to cite this article:

Darshan Halliyavar and Srividya P.2018, Tapering Interconnect Topology for High Speed Vlsi Design. Int J Recent Sci Res. 9(5), pp. 26773-26776. DOI: http://dx.doi.org/10.24327/ijrsr.2018.0905.2119

\*\*\*\*\*\*